北京电力自动化设备有限公司 ,北京 100044

摘要:本文研究基于三相四线制有源电力滤波器,对基于dq变换的软件锁相环进行了推导,并指出由于正弦函数的特点和闭环过程,系统会自动稳定在锁相正确时的运行点。研究相位和频率突变时PI参数的作用,为降低三相电压不对称和谐波对于锁相的影响,在PLL计算之前加入提取基波正序电压的环节。最后对上述内容进行仿真验证。

关键词:软件锁相环;dq变换;不对称;谐波

1 引言

实时相位是并网逆变器的基本信息,是APF有功、无功、不平衡和谐波电流跟踪控制的基准。对于电网电压相对理想或控制器计算能力较弱的应用场合,一般使用硬件电路采用过零点比较锁相,通过硬件滤波可排除谐波电压干扰。但是对于有较大基波不平衡电压的场合,硬件锁相无不平衡检测能力,只能检测某一相的相位,而不是APF要求的基波正序电压的相位,无法满足要求。并网逆变器常使用基于傅里叶变换或基于dq变换的软件锁相环,本文采用基于dq变换的三相软件锁相环。

文献[1-8]研究了基于dq的软件锁相环,其基本原理如下。

为分析方便,假设三相电压为理想基波正序电压,三相电压表达式为:

式中:ua,ub,uc表示三相电压;U表示电压峰值;ω表示电网电压基波角频率;t表示时间;θ表示初相角。

dq变换矩阵为:

式中:C表示dq变换矩阵;ω1表示dq变换矩阵的角频率,α表示dq变换矩阵的初相角。

将式(2-2)左乘式(2-1)可得:

式中:ud表示电压d轴分量;uq表示电压q轴分量。

观察式(2-3)可知,若dq变换矩阵与基波正序电压的角频率和初相角完全一致,则ud为0,即ud表示实际的锁相误差信号,因此对ud进行PI调节即可实现对于基波正序电压的锁相。锁相环基本工作原理如图2-1所示,pllpi表示ud的PI结果;2πfc表示电网额定角频率,fc一般为50Hz;ωc表示锁相的角频率;f表示锁相的实际电网频率;Ts表示开关周期,10kHz开关频率对应100μs;表示锁相的实时相角,反馈到dq变换公式。

实际上,ud为0包含两种情况,即锁相正确或锁相相差π,考虑到闭环的动态过程,锁相正确时为稳定运行点,锁相相差π时会由于计算误差等干扰信号自动运行至锁相正确的稳定运行点,利用式(2-3)和图2-1分析如下:

锁相正确时,ud=0,(ɷ-ɷ1t)+θ-α=0。假设有微小扰动使得(ɷ-ɷ1t)+θ-α>0,则ud>0,pllpi变大,ɷc变大,则ɷ1变大,最终效果使得(ɷ-ɷ1t)+θ-α变小,抵消扰动作用;假设有微小扰动使得(ɷ-ɷ1t)+θ-α<0,则ud<0,pllpi变小,ɷc变小,则ɷ1变小,最终效果使得(ɷ-ɷ1t)+θ-α变大,抵消扰动作用。可见,锁相正确时为稳定运行点。

锁相相差π时,ud=0,(ɷ-ɷ1t)+θ-α=π。假设有微小扰动使得(ɷ-ɷ1t)+θ-α>π,则ud<0,pllpi变小,ɷc变小,则ɷ1变小,最终效果使得(ɷ-ɷ1t)+θ-α更大,形成正反馈;假设有微小扰动使得(ɷ-ɷ1t)+θ-α<π,则ud>0,pllpi变大,ɷc变大,则ɷ1变大,最终效果使得(ɷ-ɷ1t)+θ-α更小,形成正反馈。

由上述分析可知,虽然ud为0包含两种情况,但由于正弦函数的特点和闭环过程,系统会自动稳定在锁相正确时的运行点。

如图2-1,锁相环稳定运行时,ud为0,ɷc为电力系统实际角频率,为实时基波正序电压相角,以下分析PI控制环节仅包含P环节或I环节时锁相动态过程。

若电压频率等于fc,相位发生突变,PI控制环节仅含P环节时,可无误差锁相。相位突增时锁相动态过程为:相位突增前pllpi=0,突增后pllpi>0,ɷc变大,相当于提高频率,相位差越接近,pllpi越小,即相角追赶速度越小,一旦相角差再次为0,pllpi恢复为0,锁相成功。相位突减动态过程类似。

若电压相位不变,频率发生突变,PI控制环节仅含P环节时,锁相结果一定有误差,但如果P参数合适,误差能小到应用时可以接受。频率突增锁相动态过程为:频率突增前pllpi=0,突增后,一方面,相角差(ɷ-ɷ1)t随时间增大;另一方面,pllpi从0开始逐渐增大,相当于提高频率,频率差越接近,pllpi增速越小,锁频成功后,pllpi保持为不变的常数,相位差固定。

若电压频率等于fc,相位发生突变,PI控制环节仅含I环节时,会形成振荡。相位突增锁相动态过程为:相位突增前

pllpi=0,突增后ud>0,pllpi从0逐渐增大,相当于提高频率,相位滞后越小, 逐渐减小,但由于积分作用,pllpi逐渐增大,即相角追赶速度越大,一旦再次相角差为0,由于pllpi>0,即锁频失败。ud从0逐渐降至谷值,同时pllpi开始减小,相角超前变大,一旦pllpi<0,ud从谷值逐渐升至0,相角差开始缩小,如此循环往复,形成振荡。

逐渐减小,但由于积分作用,pllpi逐渐增大,即相角追赶速度越大,一旦再次相角差为0,由于pllpi>0,即锁频失败。ud从0逐渐降至谷值,同时pllpi开始减小,相角超前变大,一旦pllpi<0,ud从谷值逐渐升至0,相角差开始缩小,如此循环往复,形成振荡。

若电压相位不变,频率发生突变,PI控制环节仅含I环节时,会形成振荡。频率突增锁相动态过程为:频率突增,ud从0逐渐增大对应pllpi达到锁频值之前。pllpi超过锁频值,ud逐渐减小至0,pllpi逐渐达到峰值。ud从0逐渐降至谷值,pllpi逐渐减少至锁频值。如此循环往复,形成振荡。

上文对于锁相环工作原理的分析仅针对理想电压源,APF实际应用场合则有大量不平衡和谐波分量,式(2-1)除基波正序电压对应的直流分量外还包含了基波不对称和谐波对应的交流分量,导致锁相误差甚至锁相失败[2]。

为降低不对称和谐波对于锁相的影响,本文在图2-1的基础上改进,将图4-1所示框图中输出的三相基波正序电压作为图2-1的输入。图中:dq变换和dq反变换使用电网额定频率fc对应的相位信息;udp和uqp表示dq变换结果;udp1和uqp1表示滤除大部分基波不对称和谐波对应交流分量的dq变换结果;uap1、ubp1、ucp1表示dq反变换的结果,相比输入电压ua、ub、uc已经滤除了大部分的不对称和谐波分量。由提取基波正序电压所用的dq变换和dq反变换均为固定频率fc可知,若实际电压频率为fc,图4-1的输出即为输入信号的基波正序电压分量叠加大大衰减的不平衡和谐波分量;若实际电压频率不等于fc,则图4-1的输出误差将随实际电压频率偏离fc的程度增大而增大。

5.1 理想基波正序电压

根据图2-1搭建PSCAD模型,编写代码进行仿真验证。三相电压为理想基波正序电压,U=220 V≈311V,fc=50Hz,Ts=100μs。PI环节限幅设置为±200,对应频率约±32Hz,代表相角最大追赶/等待速度。

V≈311V,fc=50Hz,Ts=100μs。PI环节限幅设置为±200,对应频率约±32Hz,代表相角最大追赶/等待速度。

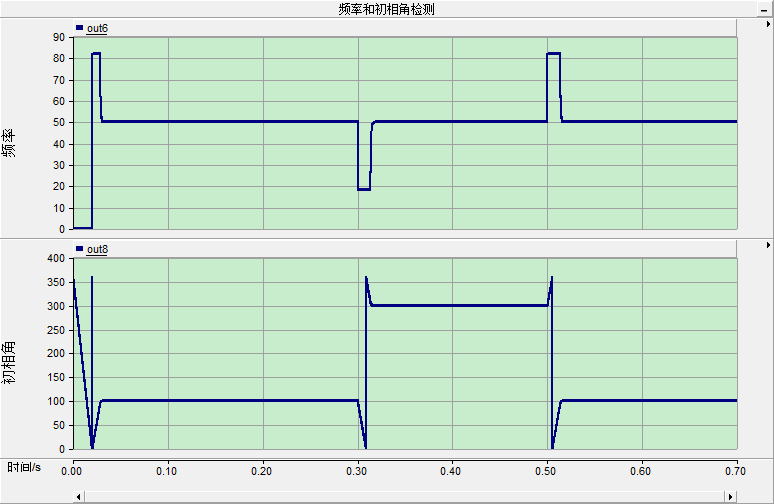

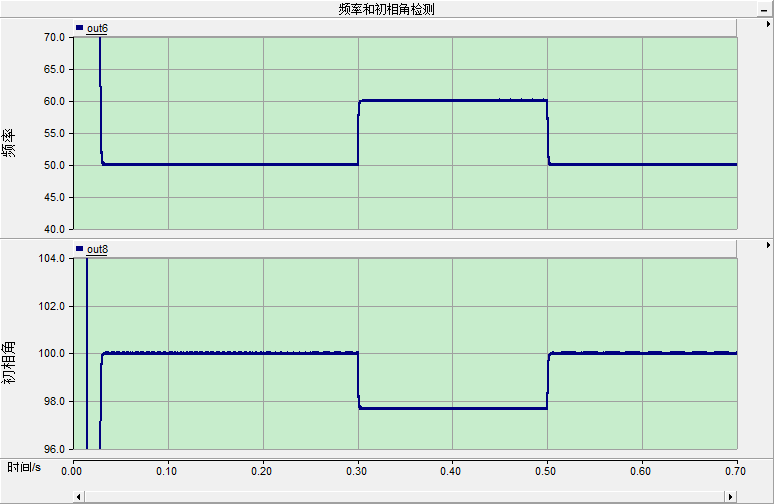

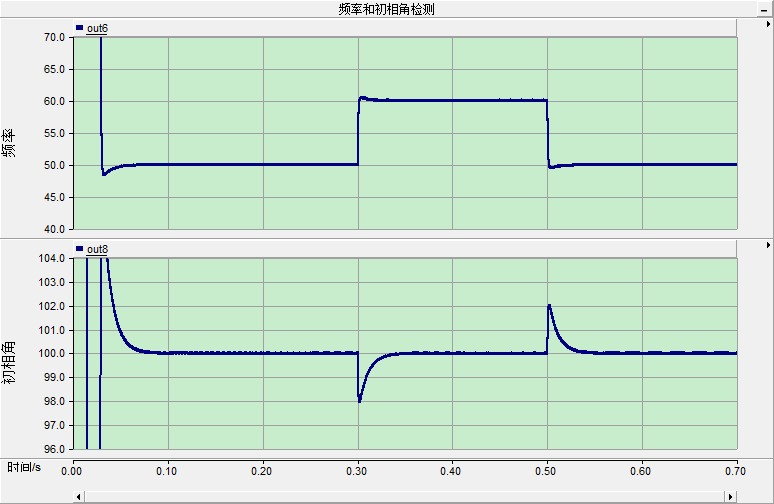

如图5-1所示,电压频率为50Hz,PI控制环节P=5,I=0,初相角突增突减,0.3s~0.5s初相角为300°,其余时间为100°,约15ms后重新锁相成功,频率和初相角检测误差均远小于1%,可认为无误差锁相,仿真结果符合第3节的分析。

如图5-2所示,电压初相角为100°,PI控制环节P=5,I=0,电压频率突增突减,0.3s~0.5s频率为60Hz,其余时间为50Hz,约3ms后重新锁相成功,频率为60Hz时,相角误差约为2.3°,频率误差始终远小于1%,其中,2.3°的相角误差对应10Hz的频率突变。仿真结果符合第3节的分析。

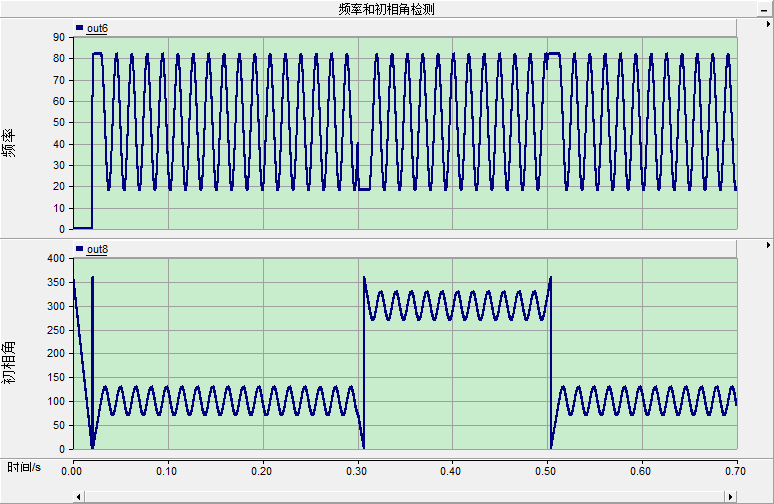

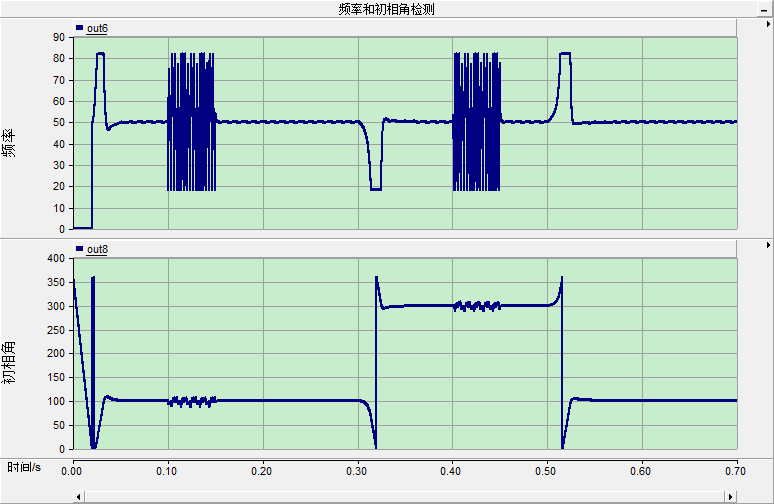

如图5-3所示,电压频率为50Hz,PI控制环节P=0,I=0.05,初相角突增突减,0.3s~0.5s初相角为300°,其余时间为100°,频率和初相角检测均出现明显振荡,锁相失败。仿真结果符合第3节的分析。

如图5-4所示,电压初相角为100°,PI控制环节P=0,I=0.05,电压频率突增突减,0.3s~0.5s频率为60Hz,其余时间为50Hz,频率和初相角检测均出现明显振荡,锁相失败。仿真结果符合第3节的分析。

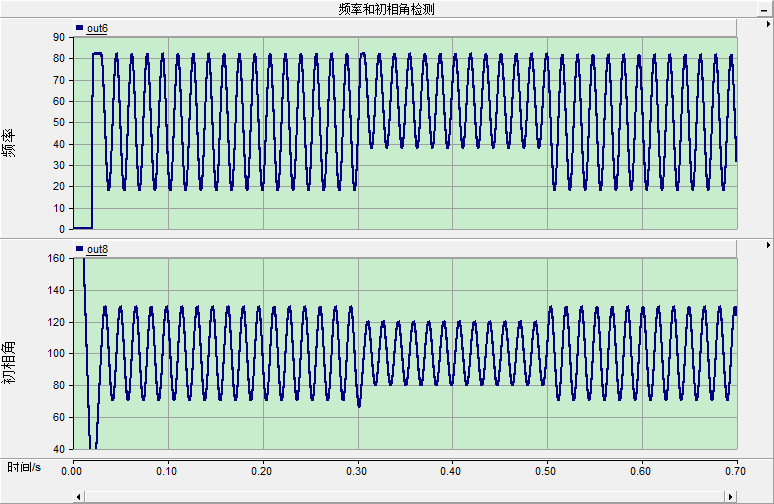

如图5-5所示,电压频率为50Hz,PI控制环节P=5,I=0.05,初相角突增突减,0.3s~0.5s初相角为300°,其余时间为100°,约15ms后重新锁相成功,锁相稳定后频率和初相角检测误差均远小于1%,可认为无误差锁相。对比图5-1可知I环节影响不大。

如图5-6所示,电压初相角为100°,PI控制环节P=5,I=0.05,电压频率突增突减,0.3s~0.5s频率为60Hz,其余时间为50Hz,约40ms后锁相成功,锁相稳定后频率和初相角检测误差均远小于1%,可认为无误差锁相。对比图5-2可见I环节消除了相角的锁相误差,但动态响应性能明显变差。

5.2 畸变电压

为验证不对称和谐波对于锁相环的影响及图4-1的效果,在三相电压中叠加基波不对称和谐波分量,各个对称分量幅值和相角如表5-1所示,不考虑基波不对称分量时,三相电压谐波畸变率约为10.8%。

仿真中PI控制环节P=5,I=0.05,0.1s~0.15s、0.4s~0.45s时图2-1所示锁相环输入为叠加基波不对称和谐波分量的三相电压

ua、ub、uc,其余时间图2-1所示锁相环输入为图4-1提取的基波正序电压uap1、ubp1、ucp1。

对称分量 | 幅值(V) | 相角(°) |

基波正序 | 220 | θ |

基波负序 | 20 | θ |

基波零序 | 20 | θ |

5次负序 | 15 | θ+40 |

7次正序 | 13 | θ+19 |

11次负序 | 9 | θ+153 |

13次正序 | 7 | θ+127 |

17次负序 | 5 | θ-124 |

19次正序 | 4 | θ-165 |

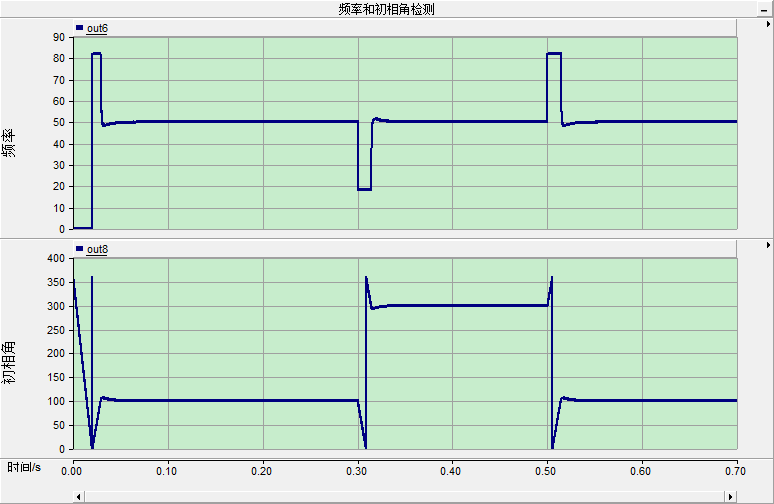

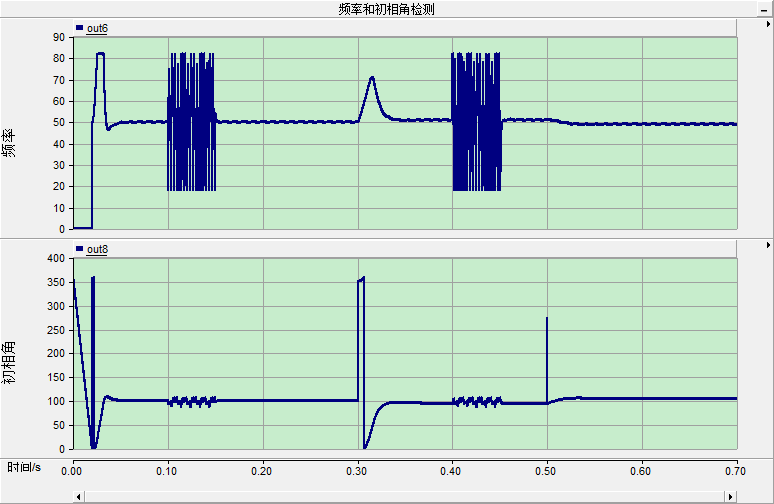

如图5-7所示,电压频率为50Hz,初相角突增突减,0.3s~0.5s初相角为300°,其余时间为100°,图2-1所示锁相环输入为叠加基波不对称和谐波分量的三相电压ua、ub、uc时,频率检测完全混乱,初相角检测波动峰峰值接近20°,锁相环无法正常工作。图2-1所示锁相环输入为图4-1提取的基波正序电压uap1、ubp1、ucp1时,约30ms后重新锁相成功,锁相稳定后频率和初相角均出现100Hz波动,初相角检测误差远小于1%,但频率检测误差较大,约为0.6%。可知电压不理想时,对于相角突变,利用图4-1改进之后的锁相环可以正常工作。

如图5-8所示,电压初相角为100°,电压频率突增突减,0s~0.3s频率为50Hz,0.3s~0.5s频率为51Hz,0.5s~0.7s频率为49Hz,图2-1所示锁相环输入为叠加基波不对称和谐波分量的三相电压ua、ub、uc时,频率检测完全混乱,初相角检测波动峰峰值接近20°,锁相环无法正常工作。图2-1所示锁相环输入为图4-1提取的基波正序电压uap1、ubp1、ucp1时,约40ms后锁相成功,锁相稳定后频率和初相角均出现100Hz波动,频率检测误差约为0.6%,50Hz时初相角检测结果为100°,51Hz时初相角检测结果为95°,49Hz时初相角检测结果为105°。可知电压不理想时,对于1Hz的频率突变,利用图4-1改进之后的锁相环可以正常工作,但初相角检测误差较大,装置性能下降。

对基于dq变换的软件锁相环进行了推导,并指出由于正弦函数的特点和闭环过程,系统会自动稳定在锁相正确时的运行点。讨论相位和频率突变时PI参数的作用。为降低不对称和谐波对于锁相的影响,在PLL计算之前加入提取基波正序电压的环节。仿真结果表明,电网电压为理想基波正序电压时,采用常规锁相环,初相角100°/300°突增突减,约15ms后重新锁相成功,电压频率50Hz/60Hz突增突减,约40ms后锁相成功,锁相稳定后频率和初相角检测误差均远小于1%;电网电压包含不平衡和谐波分量时,采用改进的锁相环,初相角100°/300°突增突减,约30ms后重新锁相成功,锁相稳定后频率和初相角检测误差均小于1%,电压频率49Hz/50Hz/51Hz突增突减,约40ms后锁相成功,频率检测误差约为0.6%,但初相角检测误差较大,装置性能下降。考虑到实际电网频率波动很小,改进的锁相环可满足工程应用。

李彦栋, 王凯斐, 卓放, 等. 新型软件锁相环在动态电压恢复器中的应用[J]. 电网技术, 2004, 28(8): 42-45.

龚锦霞, 解大, 张延迟. 三相数字锁相环的原理及性能[J]. 电工技术学报, 2009, 24(10): 94-99.

吉正华, 韦芬卿, 杨海英. 基于dq变换的三相软件锁相环设计[J]. 电力自动化设备, 2011, 31(4): 104-107.

孔雪娟, 罗昉, 彭力, 等. 基于周期控制的逆变器全数字锁相环的实现和参数设计[J]. 中国电机工程学报, 2007, 27(1): 60-64.

周卫平, 吴正国, 夏立. 基波相位和频率的高精度检测及在有源电力滤波器中的应用[J]. 中国电机工程学报, 2004, 24(4): 91-96.

王颢雄, 马伟明, 肖飞, 等. 双dq变换软件锁相环的数学模型研究[J]. 电工技术学报, 2011, 26(7):237-241.

周鹏, 贺益康, 胡家兵. 电网不平衡状态下风电机组运行控制中电压同步信号的检测[J]. 电工技术学报, 2008, 23(5): 108-113.

Changjiang.Zhan, C.Fitzer, V.K.Ramachandaramurthy, et al. Software phase-locked loop applied to dynamic voltage restorer(DVR)[C]. IEEE Power Engineering Society Winter Meeting, 2001, 3: 1033-1038.

4