中国船舶重工集团有限公司第七一〇研究所 ,湖北 宜昌 443003

摘 要: 空气放电是EMC测试中的重要一环,抗静电设计也是各类电子产品的一大难题,本文重点讨论空气放电测试时出现的一类特殊现象的整改设计,即空间耦合后的ESD设计。

关键词: 静电放电;电磁兼容;耦合;去耦合

0 引言

静电放电是电磁兼容抗扰度测试中的一项,主要依据IEC61000-4-2这一基础标准界定如何测试,包括测试仪器、测试布局、测试过程和测试结果的判定。

目前的测试主要集中在三个方面的测试:

水平耦合板HCP和垂直耦合板VCP的间接放电,这个测试模拟被测设备EUT处在强静电场下的抗扰度能力,对于有金属外壳的EUT,因为屏蔽的作用,影响不大。但对于塑料外壳的EUT,影响比较大,EUT的整个电路部分都会暴露在这个强静电场下。

被测设备EUT金属表面的直接接触放电,主要模拟静电通过金属表面泄放后,静电电流流经之处对EUT的影响,以及这一电流产生的强静电场对附近电路的影响。设计上对应的策略主要是考虑泄放路径的低阻抗和迅速泄放,以及对其他电路的隔离,对于比较敏感的电路还要考虑等电位搭接。

各类窗口缝隙的空气放电,主要模拟人手接触这些缝隙和窗口时,对EUT内部电路的放电导致的失效,这类测试主要集中在塑料外壳表电。

根据这三大类的测试,分别对应着一些设计策略,前两类的设计许多文献及书籍都有描述,也形成了一些固定的设计方法和设计理论。

本文重点讨论因为测试设备放电模式的不同而出现的耦合现象,导致EUT失效。

1 静电放电概述

静电放电现象是指具有不同静电电位的物体相互靠近或直接接触引起的电荷转移。现实中放电现象比较多,现行国际标准中将静电放电分为几大模型。

CDM模型(Charged Device Model)

电子器件在装配、传递、处理、运输等过程中,可能因器件与工作面及包装材料等接触摩擦而带电。当带电的电子器件接近或接触导体或人体时,便会产生ESD失效。由于这一放电过程是器件本身带电而引起,因此称为CDM模型。美国ESD协会标准STM5.3.1-1999规定了CDM ESD波形的校验网络、测试系统带宽、以及波形和参数。

MM模型(Machine Model)

MM模型是用来模拟带电导体对电子器件发生的静电放电,这一模型最早是日本提出,也称日本模型。美国ESD协会标准STM 5.2-2012和国际电工委员会标准IEC61340-3-2,对实验电路的典型放电电流波形和参数做了相关的规定。

HBM模型(Human Body Model)

用来模拟人体静电放电对敏感电子器件的作用,人体产生的静电是最主要的静电危害之一。美国ESD协会标准STM5.1-1999和国际电工委员会标准IEC61340-3-1对标准人体模型的电路参数,放电电流波形,还有电流参数都做了相关的规定。

IEC61000-4-2模型

IEC61000-4-2模型是在HBM模型基础上修改了人体放电电阻和放电电容单独生成的一个模型,也成为国际上用途最广泛的模型,基本原理同HBM模型。

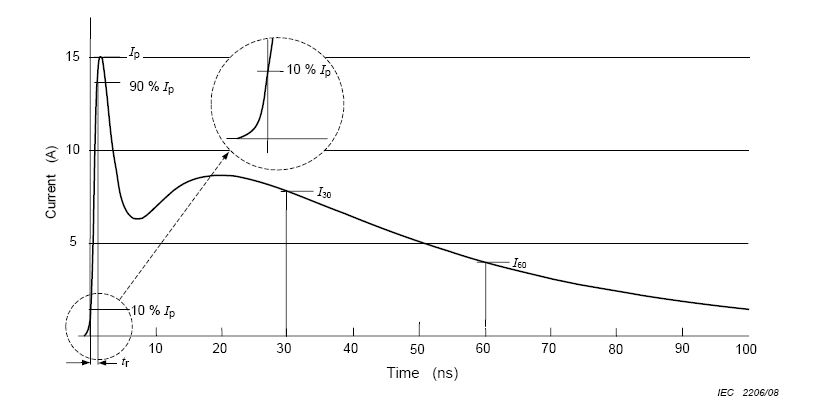

图1为IEC61000-4-2标准里典型放电电流波波形,表1列出了波形的重要校验参数,从中可以看出波形上升沿Tr非常陡峭,在0.6~1ns之间,这是所有EMS抗扰度波形中最陡峭的波形,其频谱能量理论上能覆盖到300MHz以上,从现实中的频谱仪抓取的能量来看,更能达到1GHz。

图1:IEC61000-4-2:2008 在4kV下的典型接触放电电流波形

等级 | 指示电压 kV | 放电第一个峰值电流 ±15 % A | 上升沿 tr (±25 %) ns | 在30 ns 时的电流 (±30 %) A | 在60 ns 时的电流 (±30 %) A |

1 | 2 | 7,5 | 0,8 | 4 | 2 |

2 | 4 | 15 | 0,8 | 8 | 4 |

3 | 6 | 22,5 | 0,8 | 12 | 6 |

4 | 8 | 30 | 0,8 | 16 | 8 |

表1:IEC61000-4-2:2008 波形参数

从表1中还可以看出静电电流在峰值处都比较高,这一瞬态电流流过之处,破坏性都极大,常规的MOS PN极经受不住这些冲击。静电放电的失效主要表现为两大类失效模式。

电压失效模式

静电放电电压会导致某些PIN状态位锁死,而失效。EUT主要表现某些按键或者控制信号失灵,需要系统重新启动才能恢复。

电流失效模式

静电放电电压会击穿某些MOS PN极,导致失效。EUT主要表现某些功能PIN永久性损坏,器件的SEM(电子显微镜扫描)解剖会发现,或介质击穿,或互联性熔断,或信号短路。

2 静电放电设计

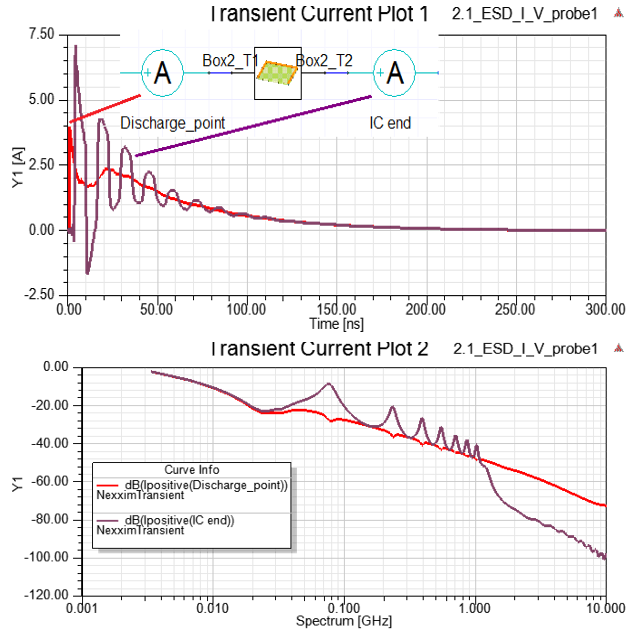

静电放电因其频谱丰富,监控手段有限,从而导致实际分析的时候比较困难,需要工程师有丰富的经验。如图2所示,放电点波形为标准的静电波形(红色线),而在IC侧,因长距离走线后变为震荡波形(紫色线),两者频谱曲线显示能量非常丰富。

图2:放电点及IC侧电流波形及频谱示意图

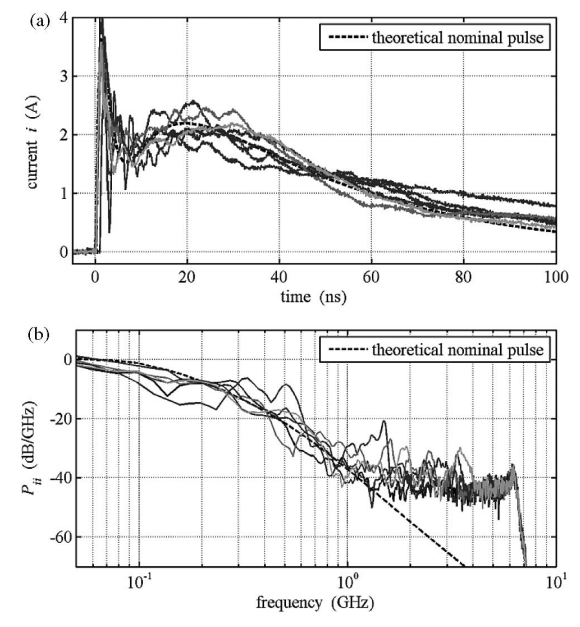

图3为国外学者Janusz Baran 和Jan Sroka在IEEE发表的论文,他们研究了六把不同的静电枪在1kV时的电流波形和频谱波形,图中所示静电放电的频谱相当丰富,在设计上也是相对难以处理。

图3:六把不同的放电枪在1kV时的电流波形及频谱示意图

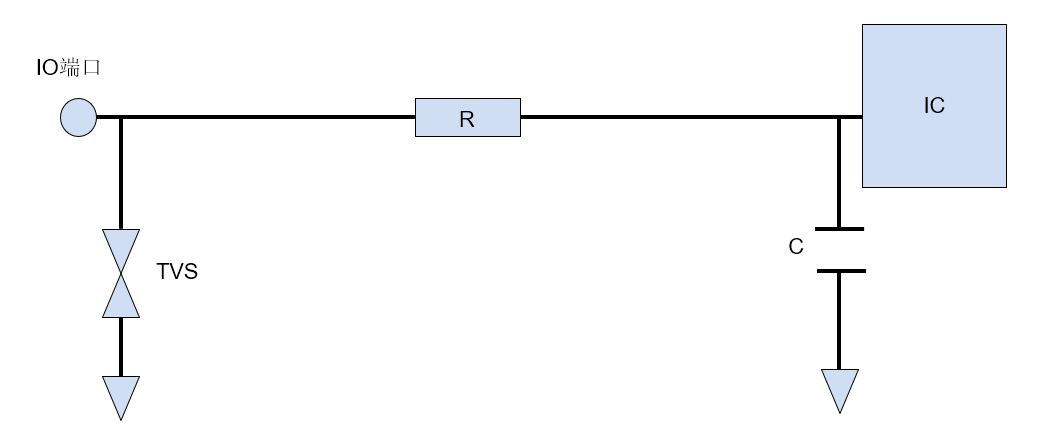

根据其失效模式,原理上有基本的整改设计对策,如图4所示。

电压失效模式下,主要思路是降低干扰电压U,对于放电点附近的电路,耦合电压比较高,宜采用TVS或者ESD高分子材料进行钳位防护。离放电点比较远的电路,因耦合电压比较低,采用电容C去耦合即可。

图4:静电放电设计原理图

电流失效模式下,因其电压在先,所以先按电压模式的设计来处理,在其基础上,串联限流电阻R,降低整个路径中的电流大小,从而减少电流破坏的风险。

实际产品设计过程,设计工程师不可能做到面面俱到,也不能对所有信号做上述的设计处理,也有一部分工程师根本不知道如何处理这些信号。后期测试时,才会发现问题,再思考如何解决问题。这时候就会产生一些经典的设计规则或者设计经验,预防产品可能出问题。

所有的RESET复位信号坚决执行图4的设计,即链路上需要配备TVS或者ESD高分子材料,各支路上串连1k以上的电阻,在各个负载端并联一个1nF电容到地,从而保护整个信号。

所有的GPIO之类的扩展信号,需要在IC侧串联电阻,如果中间连接器转连接,那么在连接器处并联电容C(容值大小根据信号频率来确定,一般10PF),串联电阻一般典型值为22ohm。

IC侧可擦写数据以及控制信号,同样按GPIO方式处理,如果是数据组可采用排阻。

低压电源采用LC滤波的方式,这个相对容易做。

模块与模块之间的互连根据其频率来做LC或者RC滤波。

3 空气放电失效的案例分析

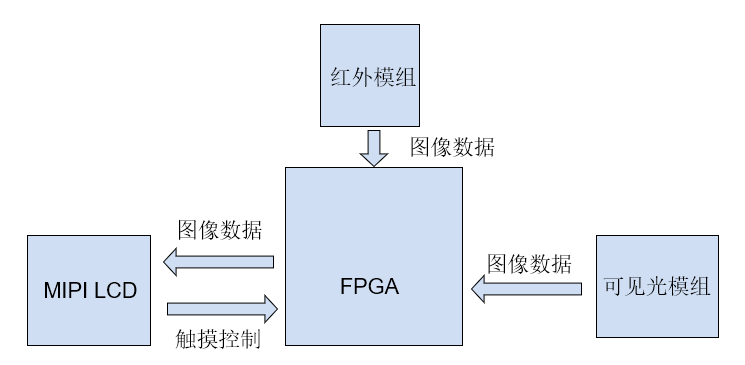

案例1是一款工业红外成像系统,他主要有四个大模块组成,如图3所示,红外模组将探测到的数据发送给主控板处理,可见光模组将摄像头常规数据发送给主控板。主控板将两组数据根据需要,叠加或者单独发送给Mipi LCD显示。每一个模组与主控板都通过FPC排线连接。他的外壳主要是塑料外壳,镜头及LCD都需要静电放电中的空气放电测试。其标准要求是8kV,实际测试时,2kV状态下,都出现图像卡死,或者直接黑屏,当静电枪头离镜头或者LCD屏较远距离时,扣动静电枪扳机,就能复现现象。

图5:案例1原理框图

静电放电主要分为三个类型:

电晕放电

电晕放电是在不均匀电场中以不击穿形式表现出来的一种气体放电,放电能量较低,在尖端电极上会呈现微弱的发光现象,并随着极间电压的升高,发光区域不断增大,在电压足够高时,呈现连续的拂尘状光体。

刷形放电

刷形放电是发生于导体和绝缘体之间的一种放电形式。其放电通道的一端具有放电集中点,另一端呈分枝状散开,并伴随放电声光。刷形放电的能量较大,声光比一般电晕放电显著。

火花放电

火花放电是两个电极间的电压足够高,致使气体全路径被击穿的一种放电形式。火花放电时,放电通道为导电性的,电极上积蓄的电荷瞬时被中和,放电火花随之消失。火花放电产生的放电电流及电磁脉冲具有较大的破坏力,它可对一些敏感的电子器件和设备造成危害。

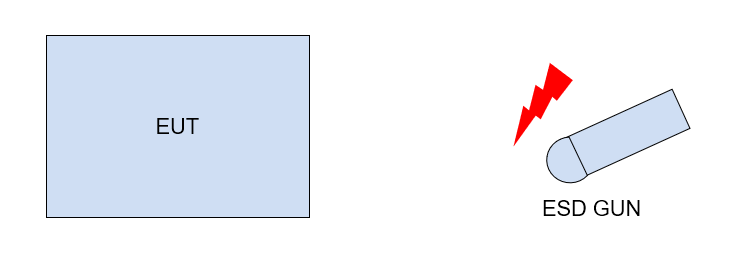

上述案例1出现现象是比较少见的,通常情况下,空气放电只有击穿介质时,才会产生火花放电,静电枪放电次数计数一次,完成一次标准的火花放电过程。但这次的现象比较特殊,并未形成火花放电,仅仅是枪头产生的电晕。如图6所示,静电枪头充满电还未靠近EUT表面,这时候EUT已经受电晕的影响,出现显示屏黑屏,或者系统死机现象,这个距离如果在5cm或者更近的距离,现象会更明显。两种计数原理不同的静电枪会出现不同的现象,静电枪1是一把国产枪,空气放电时可以连续放电,即没有击穿电离的情况下,可以连续放电,这种枪,每放一次电,EUT都会复现现象;静电枪2是一把国外进口枪,空气放电时,必须击穿电离,才会计数一次,或者电压降低到某一个点时才计数,如果这把静电枪离测试点足够远,充满电然后再迅速靠近测试点,EUT就会不出现这个现象。这两把静电枪的不同表明,静电枪充电瞬间产生的能量已经影响到了EUT,这时候不仅仅是电晕的问题。多次的重复试验表明,这两种不同机制的静电枪测试结果是不同的,这会导致在判定时出现误判。本文不去评判如何去判定,重点讨论如何从原理上去解决这种空间耦合问题。

图6:案例1 测试示意图

对于这种现象,在分析时会优先采用屏蔽法,去判断是否有电磁场能量干扰到了EUT。采用高目数的屏蔽网袋,将EUT套入其中(类似于法拉第笼),然后采用静电枪1测试空气放电,现象稍好,但测试次数增多之后,EUT会出现黑屏,或者死机现象。分析表明,EUT屏蔽后,耦合到的电磁场能量较少,不易出现问题,随着能量的累积,EUT自身不能完全消耗吸收这些能量,从而导致现象再次复现,说明EUT自身抗干扰能力较差。

根据图5,需要分析具体是哪一个模组出现问题,不论去掉红外模组还是可见光模组,原先的现象都会出现,这时候是分不清到底是哪一个部分出现问题。

将测试点固定在MIPI显示屏这侧,从显示屏这一侧先入手,这种情况下,能量会优先从显示屏耦合,然后串入系统内。降低测试电压时发现某些信号的关断或者挂死容易导致显示屏黑屏,即LCD_NPWREN和LCD_BACKLIGHT。找到这两根信号后,将这两根信号串联限流电阻和并联100PF电容,滤波之后再测试,现象会有所好转。但提高测试电压时,还是会出现现象,所以需要全局考虑问题。

针对MIPILCD显示屏我们继续做一些加强设计:

触摸屏表面加强绝缘,增加面膜设计。

触摸屏屏蔽壳体与系统地GND等电位,多点搭接。

LVDS转MIPI IC各信号优化设计,特别是滤波。

MIPI总线串联电阻限流衰减能量(早期采用并ESD器件防护)。

MIPI转换电路采用屏蔽设计。

主控板到MIPI转换板的LVDS总线串联电阻。

我们发现这些处理中,局部屏蔽的效果是有限的,因线缆太多,总会有能量直接串入到主控板,但总体MIPI显示屏不再黑屏,仅仅是系统死机。

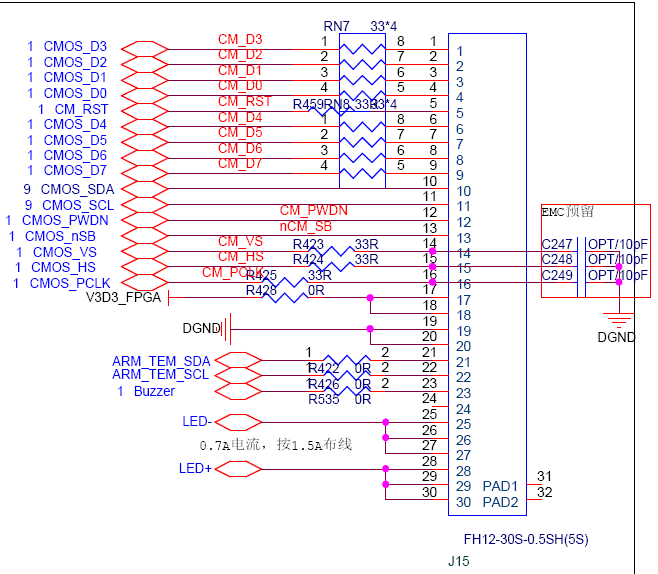

结过分析发现可见光模块容易出现问题而导致死机,将测试点移动可见光模组附件,对可见光模组做一些加强设计,如图7所示的信号组。

可见光模组采用局部屏蔽。

CMOS时钟滤波并加TVS保护。

CMOS总线做滤波。

J15排线FPC做屏蔽处理,并加磁环扣。

图7:CMOS到主板连接器

通过上述的处理,可见光部分在低测试电压状态下,明显有改善。再次深入分析发现,整体数据组预留的封装不够,一些低速信号并没有串电阻。通过示波器监控这些信号时,发现RST一直有输出,而软件上并未开通这个功能,即FPGA一直在给可见光模组复位,复位后IIC不能下发配置,导致死机。系统默认开机时下发配置,局部复位时,并不下发。针对这一点,直接拿掉了RST,事实上软件代码中并没有输出RST的命令设计,但系统在受干扰后,FPGA的RST会有主动输出,这时将查找方向全部转移到FPGA上。

针对J15继续做设计,将J15上所有的信号都串接电阻33ohm并联10pF电容,将所有传给FPGA的信号滤波保护处理后,EUT在空气放电8kV状态下测试时,工作都保持正常。J15的研究表明,系统在这一侧是非常敏感的,只要这些信号中有一两根出现影响,都会导致死机,当尝试去掉一部分信号线的串接电阻和并联电容(回归测试),测度现象很快能复现,这说明FPGA本身是比较敏感脆弱的。

至此,通过原理分析,对可见光模组和显示屏模组做整改设计,EUT在空气放电时能保持系统稳定。最后对系统做回归测试,去掉一些不重要的方案,保留了两个模组的重要设计。

4 结论

空气放电的设计在大部分产品里还是优先考虑绝缘设计,缝隙或者绝缘不够都可能导致系统故障。在设计上优先保证结构的优化,避免直接的拉弧或者击穿。优先采用绝缘或者缝隙台阶设计,或者带电件远离测试点,总体采用增加放电距离的方式来设计,保证空气放电测试通过。

本案例提到电晕放电或者充电瞬间产生的离散电磁场,在低电压场景下,对电子产品的影响通常是有限的,大部分的电子产品都直接无视这样的能量,有基本的抗干扰能力。本案的FPGA作为非常敏感的器件,在干扰下,甚至出现了连软件都没有设计的功能触发,这是非常诡异的。通过设计将远距离传输过来的若干信号衰减和滤波后,去除了干扰的影响,保证了系统的运行。本案是分模块设计,如果将可见光模组与FPGA一起放在主板上,通过多层板设计,将这些信号控制在内层,对信号品质和抗干扰能力都是一个很大的提升,即可以通过PCB优化设计来实现。

本案中用到的FPC都常规的单层FPC,在质量上相对较差,因阻抗不连续导致信号偏弱,这一点也导致系统抗干扰能力偏弱,后期设计可以采用三层FPC,增加抗干扰能力,或者采用优质的单层FPC。

本案中的等电位搭接能降低各模块之间的电位差,从而保证信号电平的稳定。空间耦合的能量被接收负载接收后第一时间需要做去耦合设计,常见的RC或LC设计是必要的手段。为了减少能量的耦合,需要对耦合传输路径加以控制,或降低环路,或破坏天线效应。原理上看,本文所述的设计主要集中在EMC设计三要素中的两个要素,即耦合路径和负载端,这两个要素的设计是EMS抗干扰设计的基本方向,工程师需要灵活应用掌握。

[参考文献]

[1] IEC61000-4-2:2008. Electromagnetic compatibility (EMC) – Part 4-2: Testing and measurement techniques – Electrostatic discharge immunity test[S].

[2] Janusz Baran,Jan Sroka. Distortion of ESD Generator Pulse Due to Limited Bandwidth of Verification Path[J]. IEEE Trans. Electromagnetic. Compat.,2010.

[3] 郑军奇.EMC(电磁兼容)设计与测试案例分析[M].电子工业出版社, 2006.

[4] D. C. Smith, Ed Nakauchi. ESD Immunity in System Designs, System Field experience, and effects of PWB layout[J]. EOS/ESD Symposium Proceeding, 2000.

[5] Ming-Dou ker,tain-Shun wu. ESD protection for submicron CMOS IC’s A tutorial[J]. CCL technical Journal,1995,Vol 42(9):10-24.