电子科技大学 电子科学与工程学院,四川 成都 610000

【摘要】 基于TSMC 0.18um RF CMOS工艺实现了一种用于电荷泵型锁相环的快速入锁结构。锁相环为数模混合电路提供稳定可靠的时钟信号,在上电与跳频过程应当越小越好,并且加速锁定过程不应当影响稳态相位噪声。快速入锁结构包括动态环路带宽单元及预置位反馈环,控制电路均采用全数字电路实现。在工作电源1.8V情况下锁定时间为1.12us,较传统结构锁定时间提升了76.7%;整体相噪在稳态保持-103.1dBc/Hz @1MHz,较传统结构仅上升了0.3%。因此,快速入锁方案能够有效降低上电启动以及跳频时的锁定时间。

关 键 词 锁相环; 快速锁定; 动态环路带宽; 预置位.

频率综合器是现代通信和信息处理系统的重要组成单元,广泛应用于空间探测、通信、雷达和计算机等领域[1]。通信系统调制解调集成芯片(Integrate Circuits)性能极大程度受限于时钟信号(Clock),其一般由外部晶体振荡器提供参考频率输入,对于内部高速时钟信号通常由锁相环电路(Phase Lock Loop)或频率综合器(Frequency Synthesizer)提供。如今的通信系统应用场合需要性能更好的时钟源以满足更高要求,故提出了一种用于低相位噪声的分数分频锁相环(PLL)的启动响应速度提高方案。

1方案设计与实现

首先,根据环路可知,其闭环传输函数可以简单表示为:

(1-1)

(1-1)

由反馈控制原理可以将式(1-1)写为一般形式,其中ωn为自然频率,ξ为阻尼系数。

(1-2)

(1-2)

假设锁相环锁定误差阈值为Δf,则锁定时间可以简单表示为:

(1-3)

(1-3)

影响跳频入锁时间的重要因素主要为环路带宽因子(ξωn)以及跳频距离Δf[2]。因为调频距离存在一个对数关系,所以环路带宽对入锁时间的贡献比调频距离更大。在上电启动阶段,系统从“0”状态开始到稳态,其跳频距离对入锁时间的影响更大。

1.1 动态环路带宽

在任意跳频阶段,环路带宽对入锁时间的影响很大,其简单表达式为:

(1-4)

(1-4)

增大环路带宽可以缩减锁定时间,而分频比和压控振荡器增益KVCO不能随意改变。故最直接的方案为改变电荷泵电流Icp和环路滤波器第一级电阻R1的值[3,4]。

动态环路带宽技术比较成熟,不做详细分析。数控电荷泵采用典型差分结构,控制电路如图1所示,其原理参考图2的时序:delay量为环路带宽切换阈值,当相位差大于delay时,CLK信号落后于D信号,此时Q=1,QN=0,控制器的输出等效于PFD的输出信号,使得CP中增流支路控制开关SW1同步TG变化。

图1 (a)环路带宽控制电路结构;(b)环路带宽控制器时序逻辑

为保证环路相位裕度,应当减小LPF的时间常数,通常改变电阻来实现。假设环路带宽增大K倍,则在电荷泵电流整体增大K2倍的情况下,LPF中的R1应该减小K倍,以此保证环路相位裕度在高环路带宽时仍保持相对合适的值。因此,电荷泵电流可由式(1-5)计算。

(1-5)

(1-5)

1.2 预置位反馈环路

此结构用于加快系统上电启动过程中的入锁速度,其简要结构如图5所示。

图2 预置位反馈环路示意结构

具体工作过程为:系统启动阶段时,SW2开关断开,环路被切断,此时VCO输出最低振荡频率。然后,digital端口送入设定值并启动PMOS上拉Vctrl电压直至超过迟滞比较器上门限电压VtH。接下来,NMOS被固定时钟驱动,此时Vctrl电压呈“阶梯式”下降,直至小于迟滞比较器下门限电压。最后,关闭控制器并闭合SW2,预置位过程结束。控制器电路如图6所示。

设定的参考控制电压量由digital端口送入DAC并随后送入迟滞比较器的负相端口,此时迟滞比较器的输出为“0”,启动PMOS上拉Vctrl电压直至超过迟滞比较器上门限电压VtH后,迟滞比较器输出跳变为“1”,至此PMOS关闭,并对NMOS送入频率固定的控制时钟,此时Vctrl电压呈“阶梯式”下降,直至小于迟滞比较器下门限电压后,迟滞比较器重新输出“0”,至此实际预置位进程基本完成。最后,关闭NMOS,闭合SW2,使得锁相环路闭合,通过环路最终实现输出时钟频率锁定。控制电路部分的DC综合网表如图6所示。

图3 预置位反馈环控制电路

2仿真结果分析

使用TSMC 0.18um RF CMOS工艺对三类结构进行瞬态仿真(Trans),其仿真数据如表1所示。

表1 三类PLL锁定时间数据对比

| 结构 | 锁定时间 | 相位噪声@1MHz |

| 传统结构 | 4.8us | -84dBc |

| 动态BW结构 | 2.8us | -96dBc |

| 复合结构 | 1.12us | -97dBc |

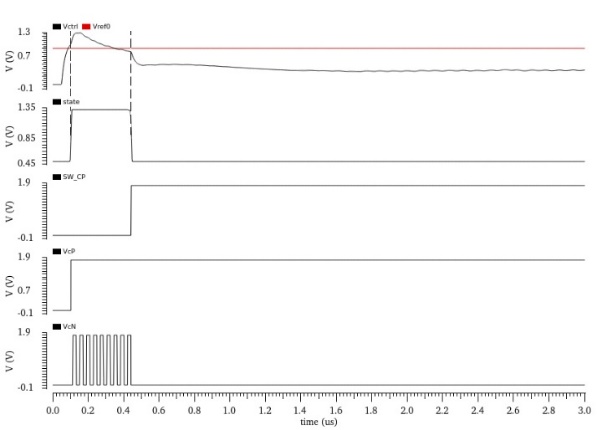

其中,复合结构的节点仿真时序如图7所示。

图4 复合快速入锁结构的控制电压曲线

仿真结果表明,传统结构的入锁时间约为4.8us,引入动态环路带宽后入锁速度提升了41.7%,但是受到电荷泵极限电流限制,初始上电过程耗时过多,且由于过大电流造成环路相位裕度下降,阻尼振荡过程时间加长。复合结构入锁时间约为1.12us,相比传统结构速度提升了76.7%。由此看出,快速入锁复合结构能够有效提高锁相环锁定速度。

3 总结

基于TSMC 0.18um RF CMOS工艺实现了一个用于加速电荷泵锁相环锁定速度的复合结构。动态环路带宽变换电路使得5ns以上相位差时提高环路带宽,预置位反馈环在上电初始化时使得在极短时间内输出频率抬升至目标频率附近。26MHz输入参考频率,输出频率为1.196GHz,综合功耗约为4mA的CP-PLL,优化后的锁定时间为1.12us,整体相噪在稳态保持-97.02dBc/Hz@1MHz。

参 考 文 献

[1] LEUNG L L K, LUONG H C. A 1 V 9.7 mW CMOS frequency synthesizer for IEEE 802.11a transceivers[J]. IEEE Trans on Microwave Theory and Techniques, 2008, 56(1): 39-47.

[2] 柏翰,余乐.锁相环锁定时间的分析与测量[J].电子世界,2016(15):110+112.

[3] 徐栋. 一种改进型快速入锁电荷泵锁相环的设计[D].苏州大学,2013.

[4] 任传阳. 快速锁定电荷泵锁相环研究与设计[D].山东大学,2016.